Researchers funded to develop a leap forward in Processor Architectures

The project proposes to produce a parallel heterogeneous 3D near-threshold computing system with unprecedented energy efficiency.

Enlarge

Enlarge

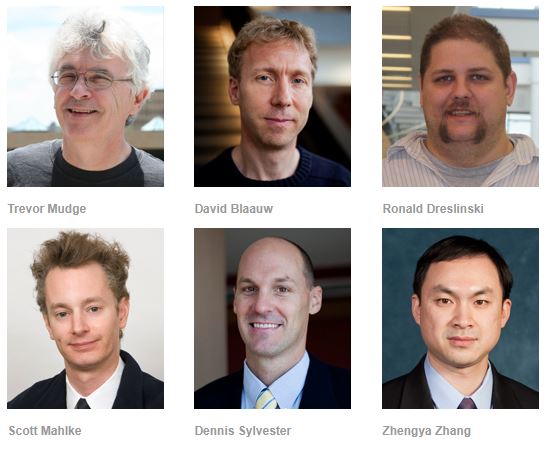

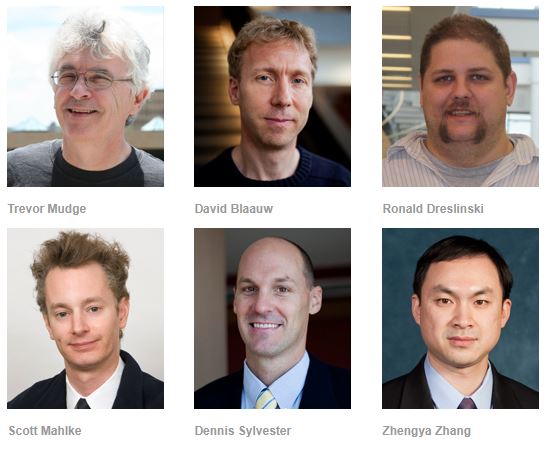

A team of researchers led by Trevor Mudge, Bredt Family Professor of Engineering and Director of the ARM Research Center at Michigan, has been awarded a contract with negotiated options of up to $5.9M for research and development of hardware and software techniques that directly support and make practical a new generation of energy efficient, high performance multi-layer processor systems for use in embedded computing systems. The grant is under DARPA’s Power Efficiency Revolution for Embedded Computing Technology (PERFECT) program.

In addition to Mudge, U-M investigators under the project include Profs. David Blaauw, Scott Mahlke, Dennis Sylvester, and Zhengya Zhang, along with Research Scientist Ronald Dreslinski. External investigators include Prof. Chaitali Chakrabarti of Arizona State University and Dr. Warren Snapp of Boeing.

The research team’s broad goal under the PERFECT program is to help develop architectures that will improve the power efficiency of embedded computing devices from today’s 1 giga floating point operation per second per watt (GFLOPS/w) to 75 GFLOPS/w. Current architectures cannot meet this goal under the current practice – known as “Moore’s Law,” of doubling circuit density every two years to increase processor speed – because of space, power, and heat dissipation constraints. It is now commonly accepted that to achieve continued performance improvements along the Moore’s Law trajectory requires significant innovations in design and technology.

Enlarge

Enlarge

The project, entitled “Energy Efficient 3D Near-Threshold Computing Systems for Future Embedded Applications,” proposes to produce a designed and simulated massively parallel heterogeneous 3D near-threshold computing system with unprecedented energy efficiency. 3D systems are processor architectures in which a number of processor cores are interconnected on and between a number of layers of silicon. Parallel systems increase efficiency by sharing operations amongst those cores. Near threshold computing (NTC) systems operate at low voltage level that is essentially the threshold of error, and are designed to compensate for inevitable low voltage errors.

The team will build upon and augment their past research projects to achieve this goal. These projects have included a 128-core parallel 3D near-threshold computing (NTC) system, known as Centip3De; a circuit technique that allows robust operation at very low voltages in processor pipelines by monitoring timing violations, known as Razor; the development of near-threshold circuit and memory technologies; open-source simulator development; and parallel compiler systems.

Enlarge

Enlarge

According to Prof. Mudge, “Applications that will benefit from the development of these systems will be computationally demanding and will often require compact or mobile form factors. Examples include intelligent, real-time search and rescue or reconnaissance systems; new forms of medical devices, such as a low-cost, handheld ultrasound system; processors to power more energy-efficient servers and data centers; and processors for automobiles that will control integrated advanced crash avoidance, navigation, multimedia, and safety systems.